我又来了= =

在精密仪表电路中,一个稳定且干净的电源是非常重要的。不稳定意味着它会在工作中发生波动,导致仪表电路工作不正常;不干净意味着其含有高频纹波与噪声,这些纹波与噪声将通过物理方式耦合到信号链中,破坏仪表电路的精确性与鲁棒性。

这次我们从纹波入手,讲解在电源电路中消除开关电源的纹波的手段和经验。

纹波(Ripple)与噪声(Noise)

噪声在我 之前的文章 中讲过了,就不啰嗦啦。

纹波(ripple) 通常指直流电源上不希望出现的交流电压变动量,一般是因为直流电经过DCDC转换器之后,输出电压的交流成分无法完全消除,残留下来的交流分量被称为Ripple。

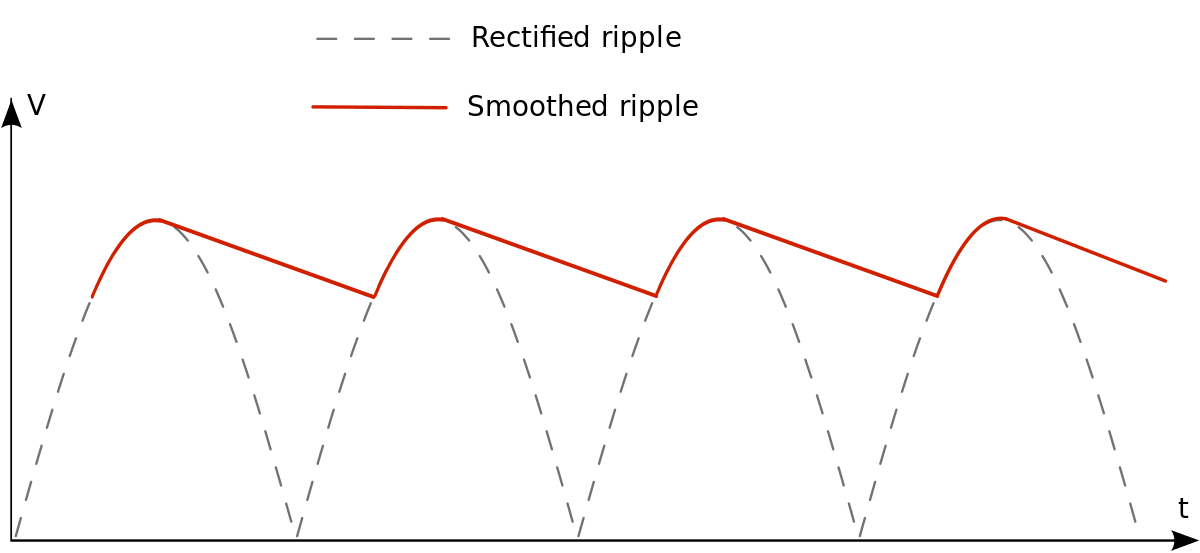

全波整流电路,在加入滤波电容之前(虚线)及之后(红色实线)的电压波形对比,交流成分未被完全消除,跨在直流之上的波纹很形象地被称为纹波(红色)。

请注意,纹波与噪声应该区分开来,将纹波直接归入噪声没啥问题,但总归是不严谨的。

关于纹波与噪声的进一步讨论,可以看这篇 e2e论坛讨论

电源抑制比

电源抑制比(Power Supply Rejection Ratio,PSRR)指某一设备对电源噪声的抑制能力。其定义是电源电压变化导致设备输出电压相应变化的比例,因为这个值挺大的,一般用对数表示,单位是dB(分贝):

\[ PSRR(dB) = 20 \log_{10}({\Delta V_{supply} \over {\Delta V_{out}}}) dB \\ 如果在放大器电路中,由于整个电路有闭环增益A_V,电源噪声会被放大,从而得出放大器本身的PSRR为: \\ PSRR(dB) = 20 \log_{10}({\Delta V_{supply} \over {\Delta V_{out}}} ·A_V) dB \\ 也就是说,噪声会被放大,计算总PSRR时应该将电路增益考虑进去。 \]

理想器件的PSRR为无穷大,即输出不随电源电压变化而变化,但这种器件当然是不存在的:(

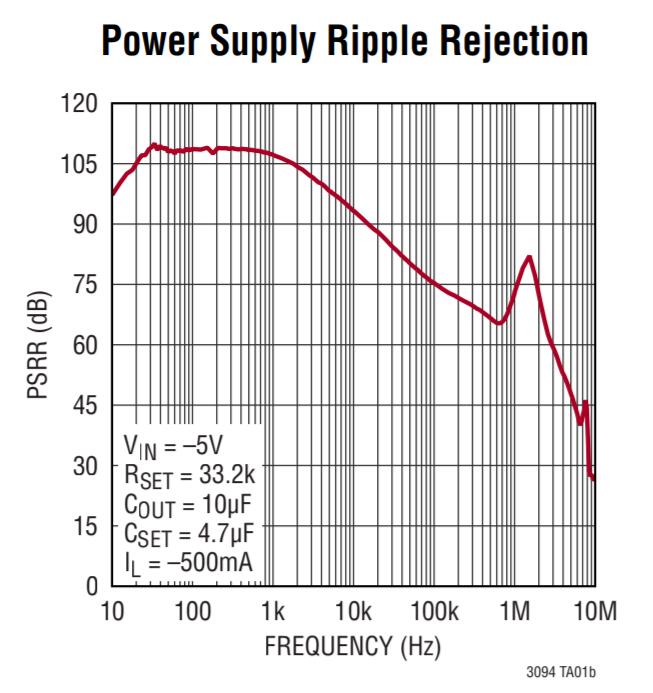

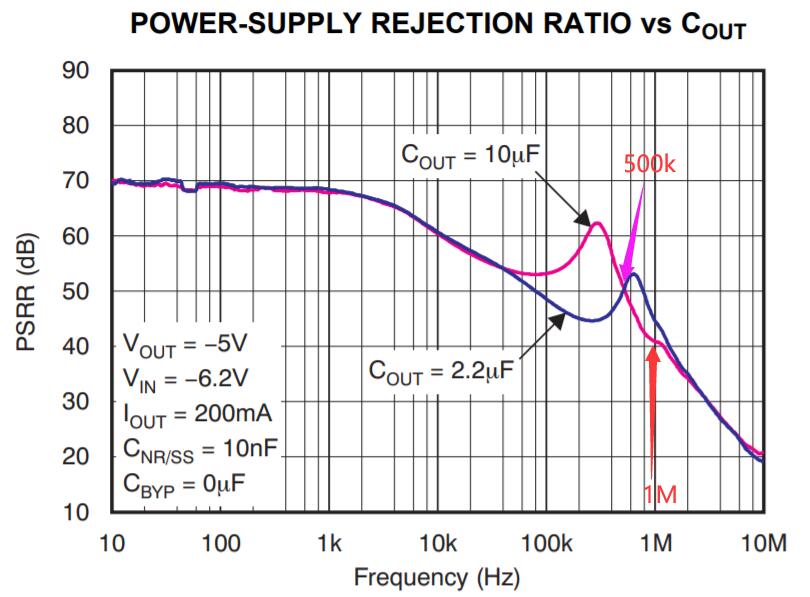

PSRR随频率而改变,一般器件的数据手册中会有一个图表用于展示该器件的PSRR在不同频率下的特性。比如下图为ADI公司的LDO-LT3094的

PSRR-f

图表,可以看出在10kHz频率以下,其PSRR大于90dB,也就是说接近或超过10万倍。在2MHz以上的频率段,其PSRR将大幅下降。

可恶的纹波!

一般地,我们的电子系统中希望有稳定的电源供应,但往往一个稳定且符合我们要求的电源不那么易得。

比如说我一个数模混合系统,使用单一5V为整个系统供电,这当然没问题,但如果模拟电路部分需要处理双极性信号(信号有负电压),我们通常有2种方法:

- 1.信号链中使用交流耦合,并为交流信号提供合适的直流偏置

- 2.使用正负电源(双电源)供电

但方法1并不是万能的,他在某些场合下有局限性。比如我们希望保留原始信号的直流成分并对其进行测量时,我们就不能使用交流耦合了。亦或者信号的参数变幻莫测,我们不能预知它的峰峰幅度等信息,不便使用单电源电路。

这时候,我们需要负电源!!!那么how?我们又有2种方法了——

- 1.供电使用变压器,输出双绕组的中间抽头作为公共地,整流可得到双电源

- 2.使用Inverting(反相)DC-DC变换器,将正电源变换得到负电源

第一种办法不是所有电路都适用的,因为变压器的体积是个大问题。而且在直流电源作为能源时,无法使用变压器。除非你再做一级DC-AC。

那么我们就开始考虑第二种方法。使用DC-DC固然是个简便的解决方案,一般也很高效,体积也很小,但是有一个致命的缺点就是 : DC-DC开关过程中会产生与开关频率相关的高频纹波,如果直接将DC-DC输出作为精密模拟电路的供电,极有可能该纹波会耦合进精密信号链中(取决于各个器件),轻则干扰有用信号,重则淹没有用信号。

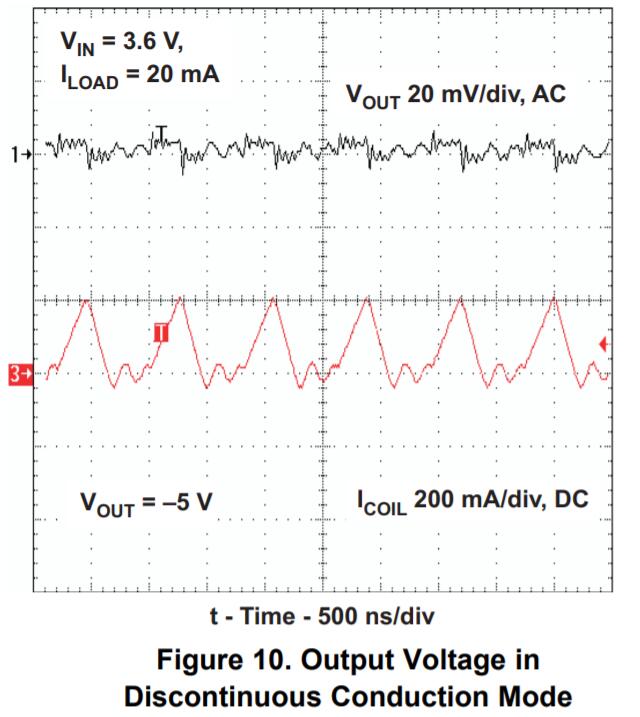

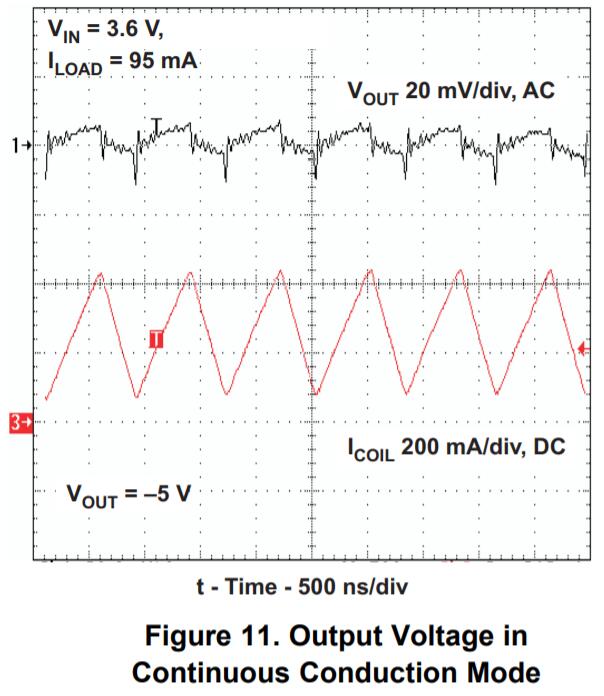

工作在不同开关模式下的TPS63700的输出电压波形

可以看到,这颗反相DC-DC将会在输出的直流电压上产生约50mV峰峰值的高频纹波。

如何干掉纹波-线性稳压器

最省心的方法是使用一颗线性稳压器或LDO去对DC-DC输出进行稳压。比如文章开头提到的 LT3094 ,它就是一颗超高PSRR(看了下感觉是业界顶尖了...)、超低噪声的低压差线性稳压器。但是要注意一点,当DC-DC的 开关频率(Switching Frequency) 落在LDO的PSRR不佳的区域时,LDO对纹波的抑制是 非常有限 的。

如下图所示,是TI的LDO TPS7A3001 的PSRR曲线,在500K频率时,其PSRR约为50dB,然而在1MHz及以上时,其PSRR骤降至40dB以下。

若该LDO输入的电源纹波频率在500KHz,该LDO还勉强能起到作用,但如果频率进一步升高,就有些不够用了。需要注意的一点是, 开关电源纹波中通常含有丰富的谐波成分!,即比如我的DC-DC开关频率为500kHz,但其输出纹波中除了500kHz的基频外,还会包含二次、三次等高次谐波。虽然500k还落在我们所期望的频率段内,但高次谐波将落入LDO的低PSRR段内,导致高次谐波的抑制效果不佳。

但如果我们选用开头那个超高PSRR的LDO,那么就不存在这个问题辣!当然,这样的代价就是money--。

如何干掉纹波-无源滤波器网络

在处理小信号时,使用RC滤波器是可选的选择。但是处理功率信号时,我们需要降低无源滤波器的输出阻抗,此时RC就不是好选择了,应考虑改用LC滤波器。(电感的直流阻抗为零)

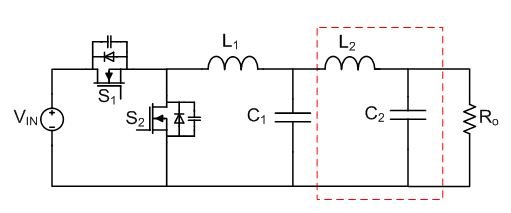

下图是ti的一篇文章,Design a second-stage filter for sensitive applications ,里面讲述了使用Buck转换器时,添加第二级LC滤波器用以减小输出的纹波。

这样做可以一定程度上衰减输出的高频能量。但我们必须谨慎选择LC的值,否则可能会得到相反的效果。 把这个电路放到系统架构中来视察,可以简化成这样:

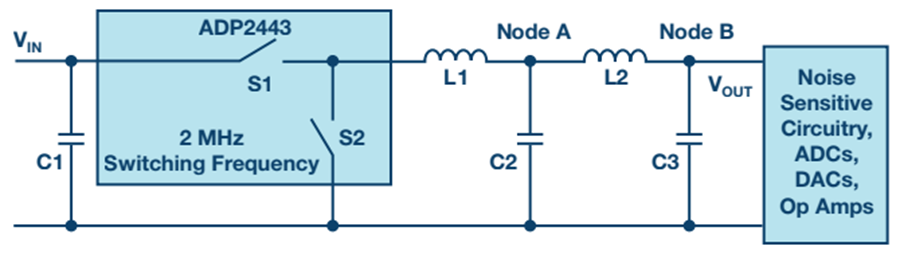

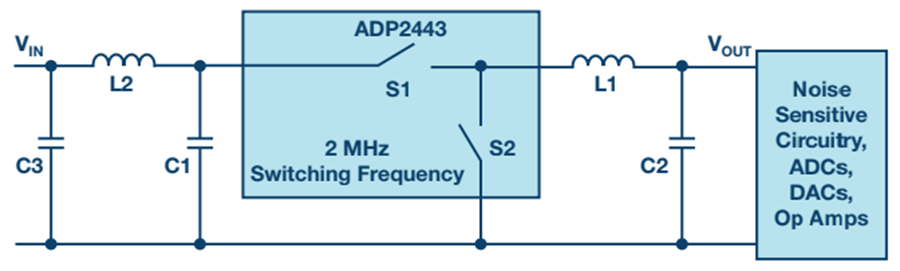

在ADI的技术文章 Switching Regulator Noise Reduction with an LC Filter 中,ADI给出了一款Buck电路的降噪方案,分别是在电路输出后级添加LC滤波器、以及在电路前后都添加LC滤波器。不过需要注意的一点是,在Buck前添加LC滤波器是很有必要的,但对于别的拓扑结构则不一定有用。因为Buck的输入端也将产生高频噪声,这个噪声可能会波及到整个电源轨道上的所有设备。

那么如何为LC滤波器选择合适的参数呢?当然需要一点点Calculation~

LC Filter Calc

来到ti的设计指南,LC

Filter Design,这篇设计指南中讲述了设计LC滤波器的过程,参考

3.1节-Output Filter Frequency Response Properties.

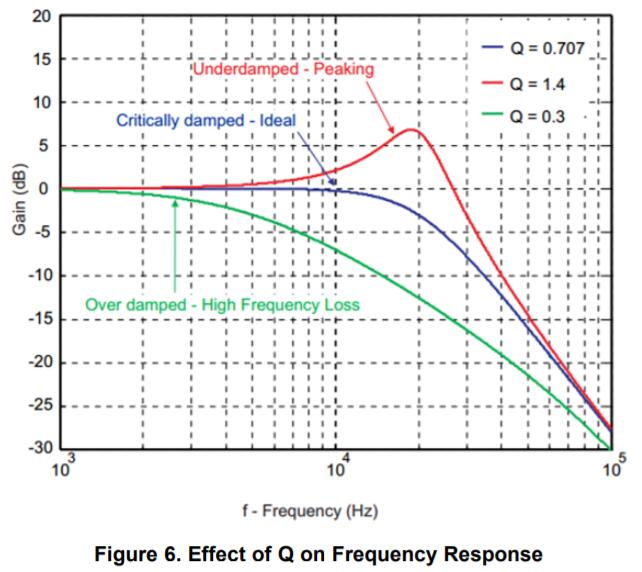

通过上面的幅频特性曲线图我们可以看到,LC电路的Q值对其幅频特性曲线的影响非常巨大,如果电路参数选择不正确,甚至还会出现增强高频噪声的情况(也就是红色曲线,Under-damped,在高频段出现了尖峰)。理想的曲线应具有ButterWorth响应类型(巴特沃斯),也就是蓝色曲线。当然,在音频滤波应用中,如果你想增强高频,也可以使用高Q值...

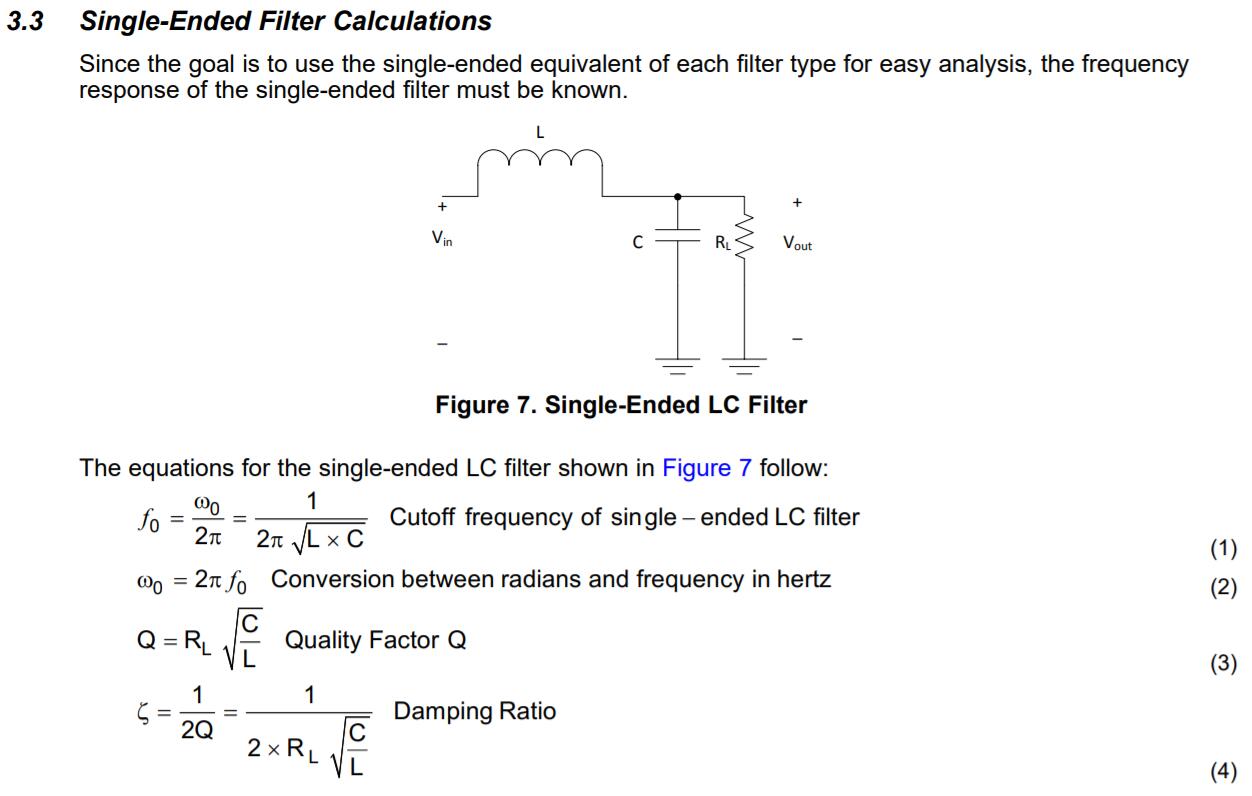

翻到计算的章节,可以看到单端LC滤波器计算如下:

可以看出,Q值由电容C、电感L和负载电阻RL共同决定。如果在未知负载电阻大小的情况下,其实挺难选的...

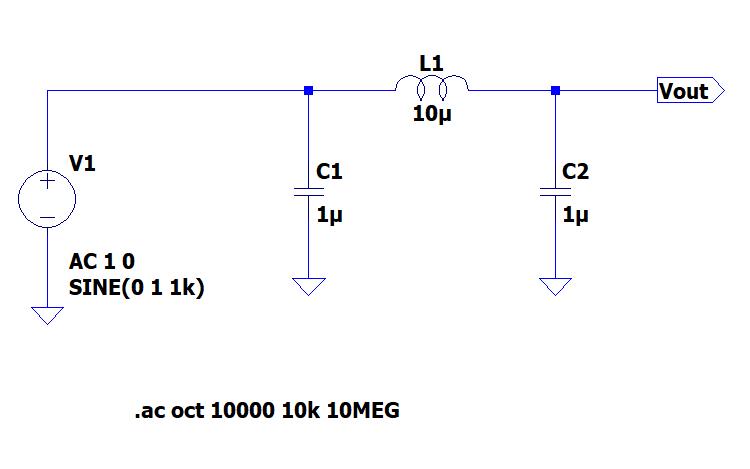

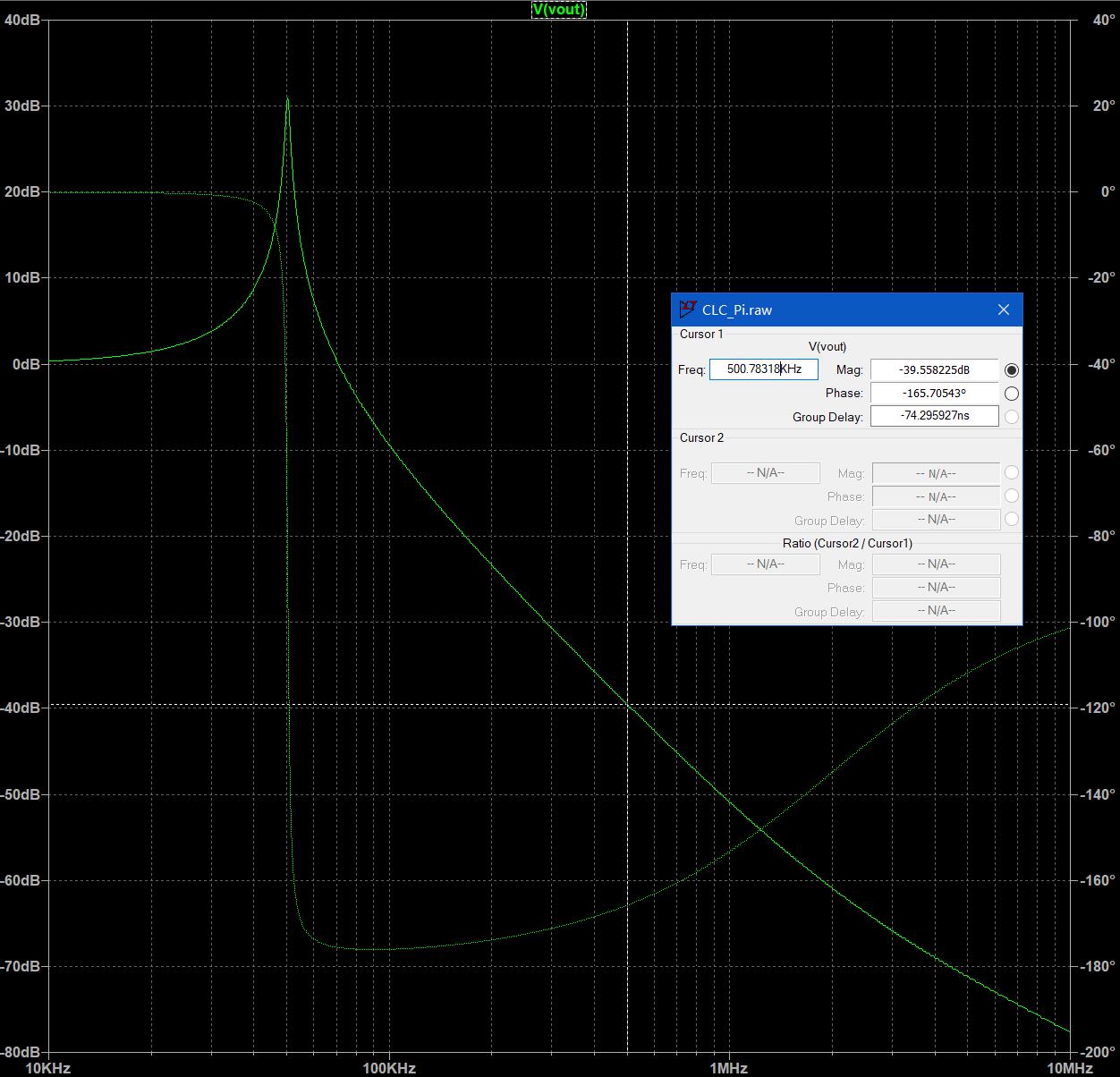

我使用LTSpice仿真了一个Π型滤波器,CLC,选值如下,在10kHz至10MHz频程内进行交流扫描分析,得到波德图如下:

可以看出,在500kHz的频率点,该滤波器的衰减约为40dB,也就是100倍电压衰减。对于开关频率为500kHz以上的开关稳压器来说,该CLC滤波器的效果应该还是不错的。不过这个电路将在约50kHz的频点达到增益峰值,约30dB增益,不过在低频段问题应该不大(赌一手我的电路里没有低频噪声...)。

陷阱(Pitfalls)!

长久以来,我们总是习惯在LDO的输入前加上电容,以此来提供最低的电源阻抗。但是在降低电源纹波的场合下,这种接法是存在问题的——我们来看个例子。

LT8614是一个Buck型开关稳压器,输出端的滤波电容为22uF(紧靠LT8614一侧)。它的开关频率为500kHz时输出的交流纹波约为20mVpp,经过十几mm的PCB铜导线连接到LT3042的输入上,这时LT3042的输出纹波仅为几uVpp。当我们在LT3042的输入端紧靠LT3042放置一个4.7uF的输入电容时(就像通常那样),输出的纹波骤增至75uVpp。(测量时开启了带宽限制20MHz,以此来去除高频尖峰)

看起来...很诡异的情况,是吧——

这并不能怪LT3042...这得怪我们的 PCB Layout。

LT3042的PSRR性能非常强劲,发生这种情况,是因为另一个物理因素的存在——

磁场

为了更好地理解磁场是如何降低LT3042的PSRR性能的,我们需要分析一下整个电路的交流通路。

Figure 21. Schematic Highlights AC Current Loop of DC-DC Converter

Together with Paths Susceptible to Magnetic Coupling.

交流电流回路由绿色环路线标识。如果在LDO端存在输入电容(也就是那个被画了叉叉的),交流电流也会通过虚线所示回路流经输入电容,LT3042的输入端对相关的交流电流呈现高阻,所以AC不会流入LT3042。

这个流经输入电容的交变电流产生了一个 磁场,这个磁场又将在相邻的小环路中产生 感生电流——就像一个变压器的2个绕组之间的关系一样。其中2个关键的环路标识在图中,分别是蓝色和红色小环路。蓝色环路由Cset和Rset构成,这个环路连通内部的误差放大器,在这个环路中产生高频交流信号将会直接作用到误差放大器的输入端,从而直接馈通至LT3042的输出。红色环路由输出电容和LDO输出阻抗组成(还有附近的负载),这里产生的高频交流成分将会直接耦合至LDO的输出。

这可能稍微有些反直觉——移除LT3042的输入电容难道不会降低LDO的性能,从而增大输出纹波吗?

考虑到这不是信号的电气馈通,而是磁耦合,在设计PCB时我们就必须谨慎地考虑器件之间的距离、屏蔽措施、以及环路方向。磁场场强和距离以及环路面积有关,所以最小化环路面积非常重要(即不在LDO前加输入电容),同时增大DC-DC与LDO的距离以减小在敏感环路中引入的高频耦合(且仅使用DC-DC的输出电容)。

这个例子生动地阐明了一点:在设计PCB时可以留下元件的保留位置,以便在实际测试时可以随时调整电路结构来测试出最佳效果应为如何。如果一开始就在LDO IC前加上了输入电容,那么我们可能会得到错误的结果——即LDO的PSRR看起来并没有手册中标注的那么高。

但是还有一点是我们难以消磨的。开关电源的输出除开纹波外,还有开关管动作时产生的 尖峰(spike)。尖峰通常是非常快速的动作过程,导致其带宽通常为上MHz级别,甚至更高。这意味着LDO的PSRR在如此高的频率下是无力的,仅用LDO是难以完全消灭这些高频尖峰的。

一种可能的方法是 结合LDO与LC滤波器 来共同完成纹波抑制。我将在不久之后的项目中实验这种方法,敬请期待~

参考

e2e论坛讨论-输出电压纹波来源和抑制

LT3094-Datasheet

TPS7A3001-Datasheet

Design

a second-stage filter for sensitive applications

Switching

Regulator Noise Reduction with an LC Filter

LC

Filter Design

AN159

- Measuring 2nV/√Hz Noise and 120dB Supply Rejection on Linear

Regulators